- Scale Integration Kecil atau (SSI) - Mengandung hingga 10 transistor atau beberapa gerbang dalam satu paket seperti AND, OR, NOT gerbang.

Sebuah Gerbang logika adalah salah satu jenis komponen elektronika yang berfungsi sebagai pengambil keputusan logika dari dua atau lebih kombinasi sinyal logika digital yang masuk pada terminal masukkannya (input), dan hanya memiliki satu buah terminal pada keluarannya (Output). Masing-masing dari komponen gerbang logika ini dapat dikombinasikan dengan beberapa buah sehingga dapat membentuk rangkaian Logika Kombinasi, rangkaian Logika Sekuensial, dan fungsi yang lain yang dapat membentuk sebuah fungsi rangkaian kombinasi logika yang lebih besar dan memiliki fungsi khusus, seperti Enkoder, Dekoder, Multiplekser, Komparator, Adder, dan lain sebagainya.

Sebagai standar komersial komponen gerbang logika digital dapat terbentuk dalam dua buah keluarga.

1. Keluarga TTL (Transistor-Transistor Logic). Biasanya di kodekan dengan Seri 7400.

2. Keluarga CMOS (Colplementary Metal-Oxide-Silicon). Dikodekan dengan Seri4000.

Notasi ini dari TTL atau CMOS mengacu pada teknologi logika yang digunakan untuk memproduksi sirkuit terpadu, (IC) atau chip "" seperti yang lebih umum disebut.

Sirkuit terpadu atau IC karena mereka lebih sering disebut, dapat dikelompokkan bersama ke dalam keluarga sesuai dengan jumlah transistor atau "gerbang" yang dikandungnya. Sebagai contoh, sebuah gerbang sederhana AND hanya berisi beberapa transistor individu, adalah sebagai sebuah mikroprosesor yang lebih kompleks mungkin berisi ribuan individu gerbang transistor. Sirkuit terpadu dikategorikan sesuai dengan jumlah gerbang logika atau kompleksitas sirkuit dalam sebuah chip tunggal dengan klasifikasi umum untuk jumlah gerbang individu diberikan sebagai:

Klasifikasi Sirkuit Terpadu (IC)

- Medium Scale Integration atau (MSI) - antara 10 dan 100 transistor atau puluhan gerbang dalam satu paket dan melakukan operasi digital seperti penambah, decoder, counter, flip-flop dan multiplexer.

- Integrasi Skala Besar atau (LSI) - antara 100 dan 1.000 transistor atau ratusan gerbang dan melakukan operasi digital tertentu seperti I / O chip, memori, aritmatika dan unit logika.

- Integrasi Skala Sangat Besar-atau (VLSI) - antara 1.000 dan 10.000 transistor atau ribuan gerbang dan melakukan operasi komputasi seperti prosesor, memori array besar dan perangkat programmable logic.

- Integrasi Skala Super Besar atau (SLSI) - antara 10.000 dan 100.000 transistor dalam satu paket dan melakukan operasi komputasi seperti keripik mikroprosesor, mikro-controller, PICs dasar dan kalkulator.

- Integrasi Skala Ultra-Large atau (ULSI) - lebih dari 1 juta transistor - anak laki-laki besar yang digunakan dalam komputer CPU, GPU, prosesor video, mikro-kontroler, FPGA dan PICs kompleks.

Hukum Moore

Pada tahun 1965, Gordon Moore co-pendiri perusahaan Intel meramalkan bahwa "Jumlah transistor dan resistor pada satu chip akan berlipat ganda setiap 18 bulan" mengenai perkembangan teknologi gerbang semikonduktor. Ketika Gordon Moore membuat jalan komentar terkenal kembali pada tahun 1965 ada sekitar hanya 60 individu gerbang transistor pada sebuah chip silikon tunggal atau mati.

Pada dunia mikroprosesor pertama pada tahun 1971 adalah Intel 4004 yang memiliki data bus 4-bit dan berisi sekitar 2.300 transistor pada satu chip, yang beroperasi di sekitar 600kHz. Saat ini, Intel Corporation telah menempatkan mengejutkan 1,2 Miliar gerbang transistor individu ke baru Quad-core i7-2700K Sandy Bridge 64-bit mikroprosesor chip yang operasi di hampir 4GHz, dan jumlah transistor on-chip masih meningkat, seperti mikroprosesor yang lebih baru lebih cepat dan mikro-controller dikembangkan.

Digital Logic State

Digital Gerbang Logika adalah blok bangunan dasar dari mana semua sirkuit elektronik digital dan sistem berbasis mikroprosesor yang dibangun dari. Dasar digital gerbang logika melakukan operasi logika AND, OR dan NOT pada bilangan biner.

Dalam desain logika digital hanya dua tingkat tegangan atau state diperbolehkan dan state ini biasanya disebut sebagai Logika "1" dan Logika "0", Tinggi dan Rendah, atau Benar dan Salah. Kedua state terwakili dalam Boolean Aljabar dan tabel kebenaran standar dengan angka biner "1" dan "0" masing-masing.

Sebuah contoh yang baik dari state digital adalah lampu sederhana seperti itu adalah baik "ON" atau "OFF" tetapi tidak keduanya pada saat yang sama. Kemudian kita dapat merangkum hubungan antara berbagai state digital sebagai:

Kebanyakan gerbang logika digital dan sistem logika digital menggunakan "logika positif", di mana tingkat logika "0" atau "LOW" diwakili oleh tegangan nol, 0V atau tanah dan tingkat logika "1" atau "TINGGI" diwakili oleh tegangan yang lebih tinggi seperti +5 volt, dengan beralih dari satu tingkat tegangan yang lain, baik dari tingkat logika "0" ke "1" atau "1" ke "0" yang dibuat secepat mungkin untuk mencegah operasi yang salah satu rangkaian logika.

Ada juga ada komplemen "Logika Negatif" sistem di mana nilai-nilai dan aturan logika "0" dan logika "1" dibalik tapi dalam bagian tutorial ini tentang gerbang logika digital kita hanya mengacu kepada logika positif konvensi sebagai itu adalah yang paling umum digunakan.

Dalam standar TTL (transistor-transistor logic) IC ada berbagai tegangan yang telah ditentukan untuk tingkat input dan tegangan output yang mendefinisikan dengan tepat apa yang logika "1" tingkat dan apa yang logika "0" tingkat dan ini ditunjukkan di bawah ini .

Ada berbagai macam jenis gerbang logika baik di bipolar 7400 dan CMOS 4000 keluarga gerbang logika digital seperti 74Lxx, 74LSxx, 74ALSxx, 74HCxx, 74HCTxx, 74ACTxx dll, dengan masing-masing memiliki kelebihan sendiri yang berbeda dan kekurangan dibandingkan dengan yang lain.

Switching tegangan yang tepat diperlukan untuk menghasilkan baik logika "0" atau logika "1" tergantung pada kelompok logika tertentu atau keluarga.

Namun, bila menggunakan pasokan +5 volt standar input tegangan TTL antara 2.0v dan 5v dianggap logika "1" atau "TINGGI" sementara setiap masukan tegangan di bawah 0.8v diakui sebagai logika "0" atau "LOW ". Tegangan wilayah di antara dua tingkat tegangan ini baik sebagai masukan atau sebagai keluaran disebut tak tentu Wilayah dan beroperasi dalam wilayah ini dapat menyebabkan gerbang logika untuk menghasilkan output yang salah.

CMOS 4000 keluarga logika menggunakan berbagai tingkat tegangan dibandingkan dengan jenis TTL seperti yang dirancang menggunakan transistor efek medan, atau FET. Dalam teknologi CMOS logika "1" tingkat beroperasi antara 3,0 dan 18 volt dan logika "0" tingkat bawah 1,5 volt.

Kemudian dari pengamatan di atas, kita dapat mendefinisikan ideal Digital Logic Gerbang sebagai salah satu yang memiliki "LOW" tingkat logika "0" 0 volt (ground) dan "TINGGI" tingkat logika "1" dari +5 volt dan ini dapat ditunjukkan sebagai:

Di mana pembukaan atau penutupan saklar menghasilkan baik tingkat logika "1" atau tingkat logika "0" dengan resistor R yang dikenal sebagai "pull-up" resistor.

Digital Logic Noise

Antara nilai-nilai TINGGI dan RENDAH didefinisikan terletak apa yang umumnya disebut "tanah tak bertuan" (area biru yang di atas) dan jika kita menerapkan tegangan sinyal dari nilai dalam lahan ini kita tidak ada yang kita tidak tahu apakah gerbang logika akan menanggapi hal itu sebagai tingkat "0" atau sebagai tingkat "1", dan output akan menjadi tak terduga.

Kebisingan adalah nama yang diberikan untuk tegangan acak dan tidak diinginkan yang diinduksi ke dalam sirkuit elektronik dengan gangguan eksternal, seperti dari switch di dekatnya, fluktuasi listrik atau dari kabel dan konduktor lain yang pick-up radiasi elektromagnetik liar. Kemudian dalam rangka untuk gerbang logika tidak menjadi pengaruh oleh kebisingan di harus memiliki sejumlah marjin suara atau kekebalan kebisingan.

Dalam contoh di atas, sinyal suara ditumpangkan ke pasokan tegangan Vcc dan selama itu tetap di atas level minimum (Von-min) input output yang sesuai dari gerbang logika tidak akan terpengaruh. Tapi ketika tingkat kebisingan menjadi cukup besar dan suara lonjakan menyebabkan tingkat tegangan TINGGI untuk turun di bawah tingkat minimum ini, gerbang logika dapat menafsirkan lonjakan ini sebagai masukan tingkat RENDAH dan beralih output sesuai memproduksi output beralih palsu. Kemudian agar gerbang logika tidak akan terpengaruh oleh suara itu harus mampu mentolerir sejumlah suara yang tidak diinginkan pada input tanpa mengubah keadaan output.

Simple Basic Digital Logic Gates

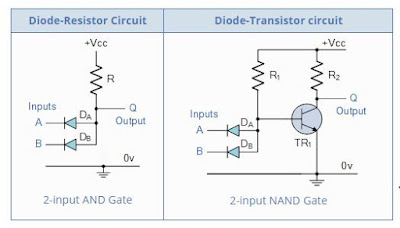

Digital gerbang logika sederhana dapat dibuat dengan menggabungkan transistor, dioda dan resistor dengan contoh sederhana dari Diode-resistor Logic (DRL) gerbang dan Diode-Transistor Logic (DTL) gerbang NAND yang diberikan di bawah ini.

Sederhana, dengan 2-masukan Diode-resistor gerbang dapat diubah menjadi sebuah gerbang NAND dengan penambahan transistor pembalik tunggal (tidak) tahap. Menggunakan komponen diskrit seperti dioda, resistor dan transistor untuk membuat logika digital sirkuit gerbang tidak digunakan dalam praktis logika tersedia secara komersial IC sebagai sirkuit ini menderita delay propagasi atau gerbang delay dan juga daya yang hilang karena resistor pull-up.

Kelemahan lain dari logika dioda-resistor adalah bahwa tidak ada "Fan-out" fasilitas yang kemampuan output tunggal untuk mendorong banyak masukan dari tahap berikutnya. Juga jenis desain tidak berubah sepenuhnya "OFF" sebagai Logic "0" menghasilkan tegangan output 0.6V (dioda drop tegangan), sehingga TTL berikut dan CMOS desain sirkuit yang digunakan sebagai pengganti.

Basic TTL Logic Gates

Diode-resistor sederhana gerbang atas menggunakan dioda terpisah untuk input, satu untuk setiap masukan. Sebagai transistor terdiri dari dua sirkuit dioda terhubung bersama-sama mewakili NPN atau perangkat PNP, dioda input dari rangkaian DTL dapat digantikan oleh satu transistor NPN tunggal dengan beberapa masukan emitor seperti yang ditunjukkan berikut ini.

Sebagai gerbang NAND berisi satu tahap pembalik NPN transistor sirkuit (TR2) tingkat output logika "1" di Q hanya hadir ketika kedua penghasil emisi TR1 terhubung ke tingkat logika "0" atau tanah yang memungkinkan arus basis untuk melewati PN junction dari emitor dan tidak kolektor. Beberapa emitter dari TR1 terhubung sebagai masukan sehingga menghasilkan fungsi gerbang NAND.

Dalam standar gerbang logika TTL, transistor beroperasi baik benar-benar di "cut off" wilayah, atau benar-benar di wilayah jenuh, Transistor sebagai operasi saklar.

Emitter-Coupled Digital Logic Gate

Emitor Coupled Logika atau ECL adalah jenis lain dari digital gerbang logika yang menggunakan transistor bipolar logika dimana transistor tidak dioperasikan di daerah saturasi, karena mereka dengan TTL standar logika digital gerbang. Sebaliknya input dan output sirkuit yang mendorong-menarik transistor terhubung dengan tegangan suplai negatif terhadap tanah.

Ini memiliki efek meningkatkan kecepatan operasi emitor digabungkan gerbang logika hingga kisaran GHz dibandingkan dengan jenis TTL standar, tapi memiliki efek noise yang lebih besar dalam ECL logika, karena transistor jenuh beroperasi dalam daerah aktif dan akan memperkuat serta sebagai sinyal switch.

Sub-keluarga Sirkuit Terpadu (IC) 74XX

Dengan perbaikan dalam desain sirkuit untuk memperhitungkan penundaan propagasi, konsumsi saat ini, fan-in dan fan-out persyaratan dll, jenis TTL teknologi transistor bipolar membentuk dasar diawali "74" keluarga logika digital IC, seperti yang "7400" Quad 2-masukan ANDgate, atau "7402" Quad 2-input gerbang OR, dll

Sub-keluarga seri 74xx IC yang tersedia yang berkaitan dengan teknologi yang berbeda yang digunakan untuk membuat gerbang dan mereka dilambangkan dengan huruf-huruf dalam antara 74 penunjukan dan jumlah perangkat. Ada sejumlah TTL sub-keluarga yang tersedia yang menyediakan berbagai macam kecepatan switching dan konsumsi daya seperti 74L00 atau 74ALS00 gerbang, "L" adalah singkatan dari "Low-power TTL" dan "ALS" singkatan "Advanced Low-power Schottky TTL" dan ini tercantum di bawah ini.

- 74xx atau 74Nxx: Standard TTL - Perangkat ini adalah keluarga TTL asli gerbang logika diperkenalkan pada awal 70-an. Mereka memiliki delay propagasi dari sekitar 10ns dan konsumsi daya sekitar 10mW.

- 74Lxx: Low Power TTL - Konsumsi daya yang meningkat selama jenis standar dengan meningkatkan jumlah resistensi internal tetapi pada biaya pengurangan kecepatan switching.

- 74Hxx: Internet Kecepatan TTL - Switching kecepatan ditingkatkan dengan mengurangi jumlah resistensi internal. Ini juga meningkatkan konsumsi daya.

- 74Sxx: Schottky TTL - Schottky teknologi yang digunakan untuk meningkatkan impedansi masukan, beralih kecepatan dan konsumsi daya (2mW) dibandingkan dengan jenis 74Lxx dan 74Hxx.

- 74LSxx: Low Power Schottky TTL - Sama seperti jenis 74Sxx tetapi dengan peningkatan resistensi internal untuk meningkatkan konsumsi daya.

- 74ASxx: Advanced Schottky TTL - Peningkatan desain lebih jenis 74Sxx Schottky dioptimalkan untuk meningkatkan kecepatan switching dengan mengorbankan konsumsi daya sekitar 22mW.

- 74ALSxx: Advanced Low Power Schottky TTL - konsumsi daya rendah sekitar 1mW dan kecepatan switching yang lebih tinggi dari sekitar 4ns dibandingkan dengan jenis 74LSxx.

- 74HCxx: Internet Kecepatan CMOS - teknologi CMOS dan transistor untuk mengurangi konsumsi daya kurang dari 1uA dengan input yang kompatibel CMOS.

- 74HCTxx: Internet Kecepatan CMOS - teknologi CMOS dan transistor untuk mengurangi konsumsi daya kurang dari 1uA tetapi telah meningkat delay propagasi dari sekitar 16nS karena input yang kompatibel TTL.

Basic CMOS Digital Logic Gate

Salah satu kelemahan utama dengan TTL digital gerbang logika seri adalah bahwa gerbang logika didasarkan pada bipolar teknologi transistor logika dan sebagai transistor adalah perangkat dioperasikan saat ini, mereka mengkonsumsi sejumlah besar listrik dari power supply +5 volt tetap.

Juga, TTL bipolar gerbang transistor memiliki kecepatan operasi terbatas ketika beralih dari "OFF" state untuk sebuah "ON" state dan sebaliknya disebut "gerbang" atau "delay propagasi". Untuk mengatasi keterbatasan ini MOS pelengkap disebut "CMOS" gerbang logika menggunakan "Field Effect Transistor" atau FET dikembangkan.

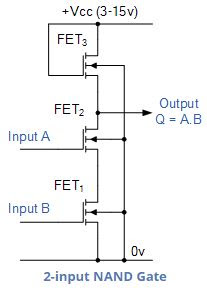

Sebagai gerbang ini menggunakan kedua P-channel dan N-channel MOSFET sebagai perangkat input mereka, pada kondisi diam tanpa switching, konsumsi daya CMOS gerbang hampir nol, (1 2UA) membuat mereka ideal untuk digunakan dalam baterai-daya rendah sirkuit dan dengan kecepatan beralih ke atas dari 100MHz untuk digunakan dalam frekuensi tinggi waktu dan komputer sirkuit.

Gerbang ini misalnya CMOS berisi 3 N-channel MOSFET, satu untuk setiap masukan FET1 dan FET2 dan satu untuk output FET3. Ketika kedua masukan A dan B berada pada tingkat logika "0", FET1 dan FET2 keduanya diaktifkan "OFF" memberikan logika output "1" dari sumber FET3.

Ketika salah satu atau kedua input berada pada tingkat logika "1" mengalir arus melalui FET sesuai memberikan keadaan keluaran ATQ setara dengan logika "0", sehingga menghasilkan fungsi gerbang NAND.

Perbaikan dalam desain sirkuit berkaitan dengan kecepatan switching, konsumsi daya yang rendah dan peningkatan penundaan propagasi telah menghasilkan standar CMOS 4000 "CD" keluarga logika IC sedang dikembangkan yang melengkapi berbagai TTL.

Seperti dengan TTL standar digital gerbang logika, semua utama gerbang logika digital dan perangkat yang tersedia dalam paket CMOS seperti CD4011, Quad 2-input gerbang NAND, atau CD4001 itu, Quad 2-masukan gerbang NOR bersama dengan semua sub-keluarga mereka.

Seperti logika TTL, MOS pelengkap (CMOS) sirkuit mengambil keuntungan dari fakta bahwa kedua N-channel dan perangkat P-channel dapat dibuat bersama-sama pada bahan substrat yang sama untuk membentuk berbagai fungsi logika.

Salah satu kelemahan utama dengan kisaran CMOS IC dibandingkan dengan jenis TTL setara mereka adalah bahwa mereka mudah rusak oleh listrik statis perawatan sehingga ekstra harus diambil ketika menangani perangkat ini. Juga tidak seperti TTL gerbang logika yang beroperasi pada tunggal + 5V tegangan untuk kedua input dan output tingkat mereka, CMOS logika digital gerbang beroperasi pada tegangan catu daya tunggal antara +3 dan +18 volt.

General CMOS Sub-keluarga meliputi:

4000B Seri: Standard CMOS - Perangkat ini adalah asli keluarga Buffered CMOS gerbang logika diperkenalkan pada awal 70-an dan beroperasi dari tegangan suplai 3,0 sampai 18V dc

74C Seri: CMOS 5V - Alat ini pin-kompatibel dengan perangkat 5V TTL standar seperti beralih logika mereka diimplementasikan dalam CMOS tetapi dengan input TTL kompatibel. Mereka beroperasi dari tegangan suplai 3,0 sampai 18V dc.

Perhatikan bahwa CMOS gerbang logika dan perangkat yang statis sensitif, jadi selalu mengambil tindakan pencegahan yang tepat bekerja pada tikar antistatik atau workbenches membumi, mengenakan gelang antistatik dan tidak menghilangkan bagian dari kemasan antistatis sampai diperlukan.

Dalam tutorial berikutnya tentang Digital Logic Gates, kita akan melihat Logika digital dan fungsi gerbang seperti yang digunakan di kedua TTL dan CMOS logika sirkuit serta yang Aljabar Boolean definisi dan kebenaran tabel.

Sumber :

http://www.electronics-tutorials.ws/logic/logic_1.html

Tidak ada komentar:

Posting Komentar